Figure 1.

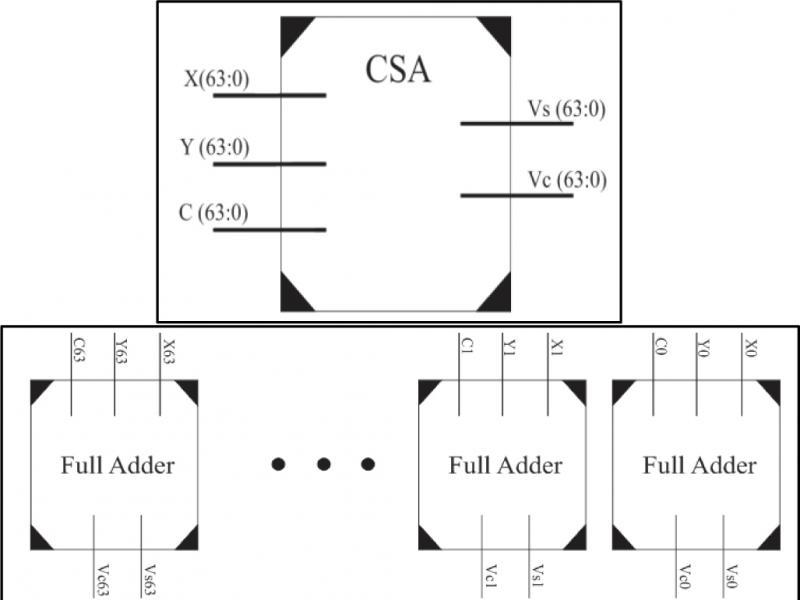

Figure 2.

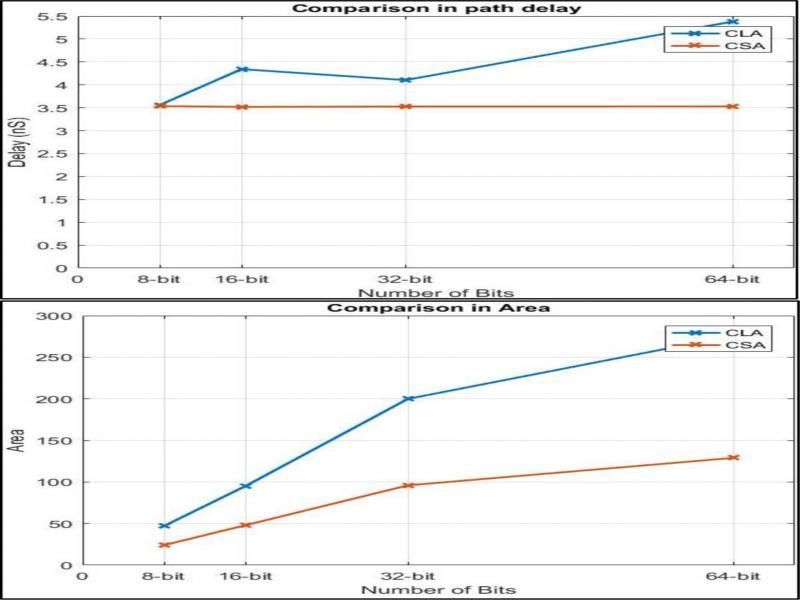

Figure 3.

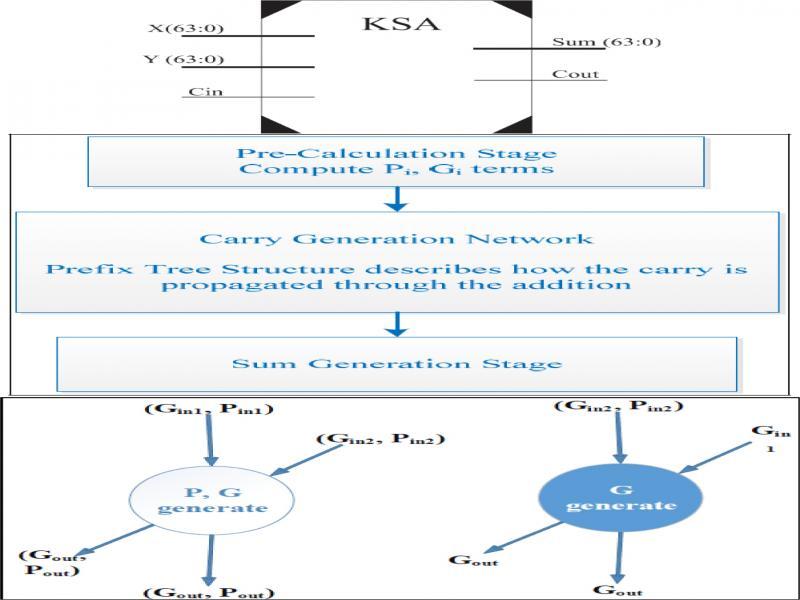

Figure 4.

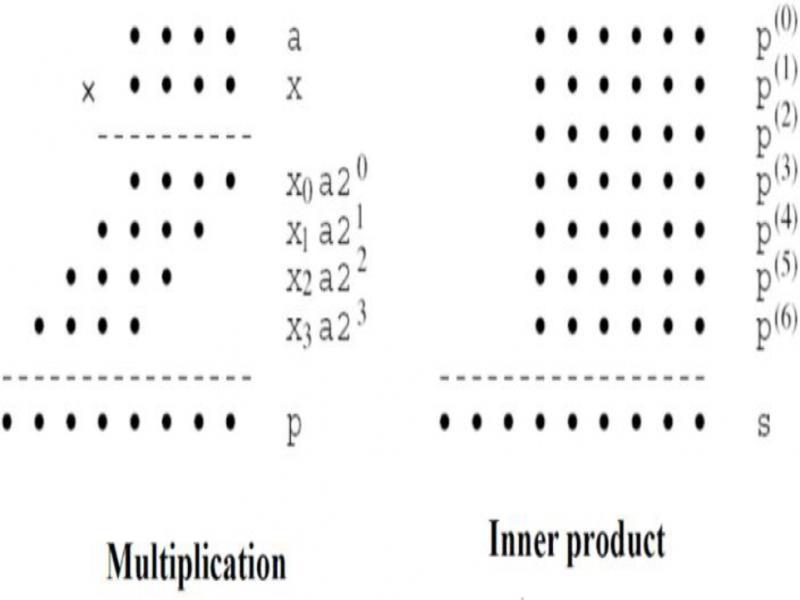

Figure 5.

Figure 6.

Figure 7.

Figure 8.

Figure 9.

Figure 10.

Figure 11.

Figure 12.

Figure 13.

Figure 14.

Figure 15.

Figure 16.

Figure 17.

COMPARISON BETWEEN DESIGN II & DESIGN III_

| Design Solutions # | Delay (gate delay) | % Optimization | Area (# of gates) | % Optimization |

|---|---|---|---|---|

| Solution I: using KSA Adder. | 23 | +15% | 6130 | |

| Solution II: using Comparator unit. | 27 | 3712 | +50% |

RADIX-8 BOOTH ENCODING_

| Inputs (bits of M-bit multiplier) | Partial Product | |||

|---|---|---|---|---|

| xi+2 | xi+1 | xi | xi−1 | PPRi |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | A |

| 0 | 0 | 1 | 0 | A |

| 0 | 0 | 1 | 1 | 2A |

| 0 | 1 | 0 | 0 | 2A |

| 0 | 1 | 0 | 1 | 3A |

| 0 | 1 | 1 | 0 | 3A |

| 0 | 1 | 1 | 1 | 4A |

| 1 | 0 | 0 | 0 | -4A |

| 1 | 0 | 0 | 1 | -3A |

| 1 | 0 | 1 | 0 | -3A |

| 1 | 0 | 1 | 1 | -2A |

| 1 | 1 | 0 | 0 | -2A |

| 1 | 1 | 0 | 1 | -A |

| 1 | 1 | 1 | 0 | -A |

| 1 | 1 | 1 | 1 | 0 |